D2417, SEPTEMBER 1980-REVISED FEBRUARY 1985

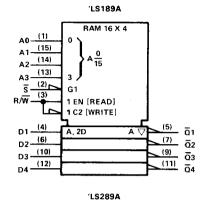

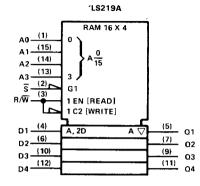

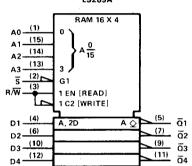

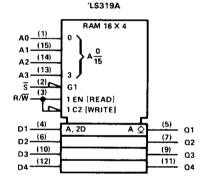

- Organized as 16 Words of Four Bits Fach

- Choice of Buffered 3-State or Open-Collector outputs

- Choice of Noninverted or Inverted Outputs

- Typical Access Time . . . 50 ns

#### description

These monolithic TTL memories feature Schottky clamping for high performance and a fast chip-select access time to enhance decoding at the system level. A three-state output version and an open-collector-output version are offered for both of the logic choices. A three-state output offers the convenience of an open-collector output with the speed of a totem-pole output; it can be bus-connected to other similar outputs, yet it retains the fast rise time characteristic of the TTL totem-pole output. An open-collector output offers the capability of direct interface with a data line having a passive pull-up.

SN54LS189A, SN54LS289A . . . J PACKAGE SN74LS189A, SN74LS289A . . . J OR N PACKAGE (TOP VIEW)

مال المال

SN54LS219A, SN54LS319A...J PACKAGE SN74LS219A, SN74LS319A...J OR N PACKAGE (TOP VIEW)

|       | _ |          |   |    |

|-------|---|----------|---|----|

| A0 🗌  | 1 | $U_{16}$ |   | ٧c |

| Ī     | 2 | 15       |   | Α1 |

| R/₩ 🛚 | 3 | 14       |   | Α2 |

| D1 [  | 4 | 13       |   | A3 |

| Q1 [  | 5 | 12       |   | D4 |

| D2 🗀  | 6 | 11       |   | Q4 |

| Q2 🗀  | 7 | 10       | D | D3 |

| GND [ | 8 | 9        | b | QЗ |

|       |   |          |   |    |

#### write cycle

Information to be stored in the memory is written into the selected address location when the chip-select  $(\overline{S})$  and the write-enable  $(R/\overline{W})$  inputs are low. While the write-enable input is low, the memory outputs are off (three-state = Hi-Z, open-collector = high). When a number of outputs are bus-connected, this off state neither loads nor drives the data bus; however, it permits the bus line to be driven by other active outputs or a passive pull-up.

#### read cycle

Information stored in the memory (see function table for input/output phase relationship) is available at the outputs when the write-enable input is high and the chip-select input is low. When the chip-select input is high, the outputs will be off.

#### **FUNCTION TABLE**

|          | INF                      | UTS |                                  | <u> </u>                         |                 |                 |  |

|----------|--------------------------|-----|----------------------------------|----------------------------------|-----------------|-----------------|--|

| FUNCTION | CHIP WRITE SELECT ENABLE |     | 'LS189A                          | 'LS289A                          | 'LS219A         | 'L\$319A        |  |

| Write    | L                        | L   | Z                                | Off                              | Z               | Off             |  |

| Read     | L                        | н   | Complement<br>of Data<br>Entered | Complement<br>of Data<br>Entered | Data<br>Entered | Data<br>Entered |  |

| Inhibit  | Н                        | Х   | Z                                | Off                              | Z               | Off             |  |

H = high level, L = low level, X = irrelevant, Z = high impedance

5

RAMs

5

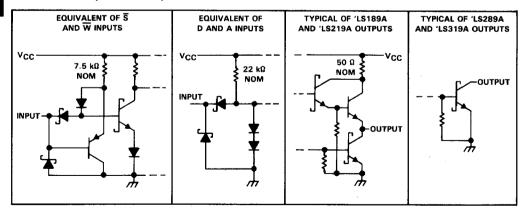

### schematics of inputs and outputs

### SN54LS189A, SN54LS219A, SN54LS289A, SN54LS319A SN74LS189A, SN74LS219A, SN74LS289A, SN74LS319A 64-BIT RANDOM-ACCESS MEMORIES

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)                       | 7 V            |

|--------------------------------------------------------|----------------|

| Input voltage                                          | 7 V            |

| Off-state output voltage: 'LS189A, 'LS219A             | 5.5 V          |

| 'LS289A, 'LS319A'                                      | 7 V            |

| Operating free-air temperature range: SN54LS' Circuits | -55°C to 125°C |

| SN74LS' Circuits                                       | 0°C to 70°C    |

| Storage temperature range                              | -65°C to 150°C |

NOTE 1: Voltage values are with respect to network ground terminal.

#### recommended operating conditions

|                |                                                           | 1    | N54LS1 |     | SN74LS189A,<br>SN74LS219A |     | UNIT |    |

|----------------|-----------------------------------------------------------|------|--------|-----|---------------------------|-----|------|----|

|                |                                                           | MIN  | NOM    | MAX | MIN                       | NOM | MAX  | 1  |

| Supply voltage | ge, VCC                                                   | 4.5  | 5      | 5.5 | 4.75                      | 5   | 5.25 | V  |

| High-level ou  | tput current, IOH                                         |      |        | - 1 |                           |     | -2.6 | mA |

| Low-level out  | tput current, IOL                                         |      |        | 12  |                           |     | 24   | mA |

| Width of writ  | te pulse (write enable low), tw(wr)                       | 100  |        |     | 70                        |     |      |    |

|                | Address before write pulse, t <sub>su(ad)</sub>           | 01   |        | •   | 01                        |     |      | 1  |

| Setup time     | Data before end of write pulse, t <sub>su(da)</sub>       | 1001 |        |     | 601                       |     |      | ns |

|                | Chip-select before end of write pulse, t <sub>SU(S)</sub> | 1001 |        |     | 601                       |     |      |    |

|                | Address after write pulse, th(ad)                         | 01   |        |     | 10                        |     |      |    |

| Hold time      | Data after write pulse, th(da)                            | 01   |        |     | 10                        |     |      | ns |

|                | Chip-select after write pulse, th(S)                      | 01   |        |     | 10                        |     |      | ]  |

| Operating fre  | e-air temperature, TA                                     | - 55 |        | 125 | 0                         |     | 70   | °C |

11The arrow indicates the transition of the write-enable input used for reference: 1 for the low-to-high transition, 1 for the high-to-low transition.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise

|      | PARAMETER TEST CONDITIONS <sup>†</sup> |                                                                             |          | N54LS1           |       |     | 9A<br>9A | UNIT  |                 |

|------|----------------------------------------|-----------------------------------------------------------------------------|----------|------------------|-------|-----|----------|-------|-----------------|

|      |                                        |                                                                             | MIN      | TYP <sup>‡</sup> | MAX   | MIN | TYP‡     | MAX   |                 |

| VIH  | High-level input voltage               |                                                                             | 2        |                  |       | 2   |          |       | V               |

| VIL  | Low-level input voltage                |                                                                             |          |                  | 0.7   | L   |          | 0.8   |                 |

|      | Input clamp voltage                    | $V_{CC} = MIN$ , $l_1 = -18 \text{ mA}$                                     |          |                  | - 1.5 |     |          | 1.5   | V               |

| Vон  | High-level output voltage              | $V_{CC} = MIN$ , $V_{IH} = 2 V$ ,<br>$V_{IL} = V_{IL} max$ , $I_{OH} = MAX$ | 2.4      | 3.1              |       | 2.4 | 3.1      |       | ٧               |

|      |                                        | V <sub>CC</sub> = MIN, V <sub>IH</sub> = 2 V, I <sub>OL</sub> = 12 mA       |          | 0.25             | 0.4   |     | 0.25     | 0.4   | V               |

| VOF  | Low-level output voltage               | V <sub>IL</sub> = V <sub>IL</sub> max I <sub>OL</sub> = 24 mA               |          |                  |       |     | 0.35     | 0.5   | L.              |

|      | Off-state output current               | V <sub>CC</sub> = MAX, V <sub>IH</sub> = 2 V,                               |          |                  | 20    | }   |          | 20    | μA              |

| OZH  | high-level voltage applied             | $V_{IL} = V_{IL} max$ , $V_{O} = 2.7 V$                                     |          |                  |       |     |          |       | <u></u>         |

|      | Off-state output current,              | $V_{CC} = MAX$ , $V_{IH} = 2 V$ ,                                           |          |                  | - 20  |     |          | - 20  | μА              |

| OZL  | low-level voltage applied              | $V_{1L} = V_{1L}max$ , $V_{0} = 0.4 V$                                      | <u> </u> |                  |       |     |          |       | <u> </u>        |

| I.   | Input current at                       | V <sub>CC</sub> = MAX, V <sub>I</sub> = 7 V                                 |          |                  | 100   |     |          | 100   | μΑ              |

| lj.  | maximum input voltage                  | VCC = IMAX, VI / /                                                          |          |                  |       | ļ   |          |       | ļ .             |

| ηн   | High-level input current               | $V_{CC} = MAX$ , $V_{I} = 2.7 V$                                            | 1        |                  | 20    |     |          | 20    | μА              |

| TIL. | Low-level input current                | $V_{CC} = MAX$ , $V_I = 0.4 V$                                              |          |                  | -0.4  | 1   |          | -0.4  | mA              |

|      | Short-circuit output                   | V <sub>CC</sub> = MAX                                                       | - 30     |                  | - 130 | -30 |          | - 130 | l <sub>mA</sub> |

| los  | current <sup>§</sup>                   | VCC - MIAN                                                                  | 100      |                  |       | L.  |          |       |                 |

| lcc  | Supply current                         | V <sub>CC</sub> = MAX, See Note 2                                           | 1        | 35               | 60    |     | 35       | 60    | mA              |

<sup>&</sup>lt;sup>1</sup>For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

# switching characteristics over recommended operating ranges of TA and VCC (unless otherwise noted)

| PARAMETER |                                          | PARAMETER TEST CONDITIONS |                         |      |     | 189A<br>219A |                  | 9A<br>9A | UNIT |    |

|-----------|------------------------------------------|---------------------------|-------------------------|------|-----|--------------|------------------|----------|------|----|

|           |                                          |                           | MIN                     | TYP‡ | MAX | MIN          | TYP <sup>‡</sup> | MAX      |      |    |

| ta(ad)    | Access time from address                 | 5.A                       | 0 45.5                  |      | 50  | 90           |                  | 50       | 80   | ns |

| u\uu,     | Access time from chip select (enabl      | e time)                   | C <sub>L</sub> = 45 pF, |      | 35  | 70           |                  | 35       | 60   | ns |

| tSR       | Sense recovery time                      |                           | See Note 3              |      | 55  | 100          |                  | 55       | 90   | ns |

| -311      |                                          | from S                    | $C_L = 5 pF$ ,          |      | 30  | 60           |                  | 30       | 50   | Ι  |

| tPXZ      | tpxz Disable time from high or low level | from R/W                  | See Note 3              |      | 40  | 70           |                  | 40       | 60   | ns |

$<sup>^{\</sup>ddagger}AII$  typical values are at VCC = 5 V, TA = 25 °.

NOTE 3: Load circuits and voltage waveforms are shown in Section 1.

<sup>&</sup>lt;sup>‡</sup>All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C. §Not more than one output should be shorted at a time and duration of the short circuit should not exceed one second.

NOTE 2: ICC is measured with the write-enable and chip-select inputs grounded, all other inputs at 4.5 V, and all outputs open.

## SN54LS289A, SN54LS319A, SN74LS289A, SN74LS319A 64-BIT RANDOM-ACCESS MEMORIES WITH OPEN-COLLECTOR OUTPUTS

#### recommended operating conditions

|               |                                                           |      | N54LS2<br>N54LS3 |     | SN74LS289A,<br>SN74LS319A |     |                          | UNIT |

|---------------|-----------------------------------------------------------|------|------------------|-----|---------------------------|-----|--------------------------|------|

|               | •                                                         | MIN  | NOM              | MAX | MIN                       | NOM | MAX                      |      |

| Supply voltag | ge, V <sub>CC</sub>                                       | 4.5  | 5                | 5.5 | 4.75                      | 5   | 5.25                     | ٧    |

| High-level ou | tput voltage, VOH                                         |      |                  | 5.5 |                           |     | 5.5                      | ٧    |

| Low-level out | tput current, IOL                                         |      |                  | 12  |                           |     | 24                       | mΑ   |

| Width of writ | te pulse (write enable low), t <sub>W(Wr)</sub>           | 100  |                  |     | 70                        |     |                          |      |

|               | Address before write pulse, t <sub>su(ad)</sub>           | 01   |                  |     | 01                        |     |                          |      |

| Setup time    | Data before end of write pulse, t <sub>su(da)</sub>       | 1001 |                  |     | 601                       |     |                          | ns   |

|               | Chip-select before end of write pulse, t <sub>SU(S)</sub> | 1001 | <del></del>      |     | 601                       |     | 9A<br>MAX<br>5.25<br>5.5 | 1    |

|               | Address after write pulse, th(ad)                         | 10   |                  |     | 01                        |     |                          |      |

| Hold time     | Data after write pulse, th(da)                            | 10   |                  |     | 01                        |     |                          | ns   |

|               | Chip-select after write pulse, th(S)                      | 01   |                  |     | 01                        |     |                          |      |

| Operating fre | e-air temperature, TA                                     | - 55 |                  | 125 | 0                         |     | 70                       | °C   |

<sup>11</sup>The arrow indicates the transition of the write-enable input used for reference: 1 for the low-to-high transition, 1 for the high-to-low transition.

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|     | PARAMETER                              | TEST CONDITIONS†                       |                        |                         | SN54LS289A<br>SN54LS319A |                  |       | SN74LS289A<br>SN74LS319A |                  |      | UNIT |

|-----|----------------------------------------|----------------------------------------|------------------------|-------------------------|--------------------------|------------------|-------|--------------------------|------------------|------|------|

|     |                                        |                                        |                        |                         | MIN                      | TYP <sup>‡</sup> | MAX   | MIN                      | TYP <sup>‡</sup> | MAX  |      |

| VIH | High-level input voltage               |                                        |                        |                         | 2                        |                  |       | 2                        |                  |      | >    |

| VIL | Low-level input voltage                |                                        |                        |                         |                          |                  | 0.7   |                          |                  | 0.8  | V    |

| VIK | Input clamp voltage                    | VCC = MIN, I                           | = -18 m/               | 4                       |                          | •                | - 1.5 |                          |                  | -1.5 | V    |

| 1   | Ui-b land and a second                 | V <sub>CC</sub> = MIN, V               | / <sub>IH</sub> = 2 V, | $V_0 = 2.4 \text{ V}$   |                          |                  | 20    |                          |                  | 20   |      |

| ІОН | High-level output current              | V <sub>IL</sub> = V <sub>IL</sub> max, |                        | $V_0 = 5.5 V$           |                          |                  | 100   |                          |                  | 100  | μА   |

| 1/  | I am land antant malage                | V <sub>CC</sub> = MIN, V               | / <sub>IH</sub> = 2 V, | I <sub>OL</sub> = 12 mA |                          | 0.25             | 0.4   |                          | 0.25             | 0.4  | V    |

| VOL | Low-level output voltage               | V <sub>IL</sub> = V <sub>IL</sub> max  |                        | IOL = 24 mA             |                          |                  |       |                          | 0.35             | 0.5  | ٠    |

| lμ  | Input current at maximum input voltage | V <sub>CC</sub> = MAX, \               | / <sub>I</sub> = 7 V   |                         |                          |                  | 100   |                          |                  | 100  | μΑ   |

| ΊΗ  | High-level input current               | VCC = MAX, V                           | $I_1 = 2.7 \text{ V}$  |                         |                          |                  | 20    |                          |                  | 20   | μA   |

| ΊL  | Low-level input current                | VCC = MAX, \                           | / <sub>I</sub> = 0.4 V |                         |                          |                  | -0.4  |                          |                  | -0.4 | mA   |

| Icc | Supply current                         | V <sub>CC</sub> = MAX, S               | See Note 2             |                         |                          | 35               | 60    |                          | 35               | 60   | mA   |

<sup>†</sup>For-conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

#### switching characteristics over recommended operating ranges of TA and VCC (unless otherwise noted)

|                   | PARAMETER                                  |          | TEST CONDITIONS                         |     | SN54LS289A<br>SN54LS319A |     |     | SN74LS289A<br>SN74LS319A |     |    |  |

|-------------------|--------------------------------------------|----------|-----------------------------------------|-----|--------------------------|-----|-----|--------------------------|-----|----|--|

|                   |                                            |          |                                         | MIN | TYP <sup>‡</sup>         | MAX | MIN | TYP‡                     | MAX | 1  |  |

| ta(ad)            | Access time from address                   | s        |                                         |     | 50                       | 90  |     | 50                       | 80  | ns |  |

| t <sub>a(S)</sub> | Access time from chip se<br>(enable time)  |          | $C_L = 45 \text{ pF}, R_L = 667\Omega,$ |     | 35                       | 70  |     | 35                       | 60  | ns |  |

| tSR               | Sense recovery time                        |          | See Note 3                              |     | 55                       | 100 |     | 55                       | 90  | ns |  |

| <sup>t</sup> PLH  | Propagation delay time,                    | from S   |                                         |     | 30                       | 60  |     | 30                       | 50  |    |  |

|                   | low-to-high-level<br>output (disable time) | from R/W |                                         |     | 40                       | 70  |     | 40                       | 60  | ns |  |

$<sup>^{\</sup>ddagger}$ All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°.

NOTE 3: Load circuits and voltage waveforms are shown in Section 1.

<sup>&</sup>lt;sup>‡</sup>All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C.

Not more than one output should be shorted at a time and duration of the short circuit should not exceed one second.

NOTE 2: I<sub>CC</sub> is measured with the write-enable and chip-select inputs grounded, all other inputs at 4.5 V, and all outputs open.